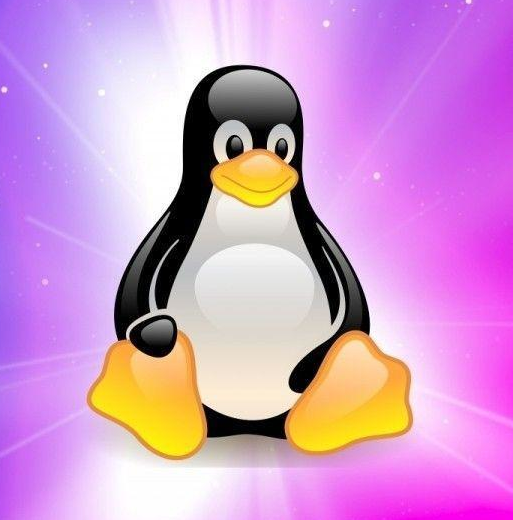

A Basil Plant

InfoSec Person | Alt-Account#2

- 4 Posts

- 43 Comments

I’m sending this to the guy in the photo :D

(I use Debian on all my machines BTW)

I do use Signal quite a bit. Some important contacts don’t use it and hence, you see my using of WhatsApp.

Yep! Series 4 hasn’t “released” on YouTube yet. I saw Paul William’s story on instagram that they’re releasing Series 5 on TV, but sadly I don’t have access to that. I’m fine being behind by 1-2 years though.

I’m a huge fan of the original British TM, but TM New Zealand is honestly amazing. The whole thing is available on YouTube (thanks Little Alex Horne + team!!!).

In my and many of my friends’ opinion, TM New Zealand Series 2 is one of the best TM series. TM New Zealand in general is absolutely unhinged.

Series 1 feels a bit off, which is probably because it’s unlike British TM. I got used to it fairly quick though.

TM NZ Series 3 (final episode releases on YouTube in 2-3 days)

3·3 months ago

3·3 months agoThis website shows the SearXNG public instances. It is updated every 24 hours, except the response times which are updated every 3 hours. It requires Javascript until the issue #9 is fixed.

0·4 months ago

0·4 months agoI think the difference lies in two things:

-

You can share an article from a user of a different instance. In this case, your instance will have to look up the rel=“author” tag and check whether the URL is a fediverse instance. I’m not sure whether this is scalable as compared to a tag that directly indicates that the author is on the fediverse. Imagining a scenario where there are 100, 1000, 10,000, or 100,000 instances on different versions.

-

The tag is to promote that the author is on the fediverse. If the rel=“author” tag points to twitter for example, maybe Eugen Rochko + team didn’t want a post on the fediverse to link to twitter.

These are my thoughts and idk if they’re valid. But I think just reusing the rel=“author” isn’t the most elegant solution.

I know that mastodon already uses rel=“me” for link verification (I use it on mu website + my mastodon account), but that’s a different purpose - that’s more for verification. There’s still no way of guaranteeing that the rel=“author” tag points to a fediverse account. You’re putting the onus on the mastodon instance.

-

0·4 months ago

0·4 months agoIt works in a pretty neat way:

We’ve decided to create a new kind of OpenGraph tag—the same kind of tags you have on your website to determine which thumbnail image will appear on the preview for the page when shared on Discord, iMessage, or Mastodon. It looks like this: <meta name=“fediverse:creator” content=“@[email protected]” />.

via: https://blog.joinmastodon.org/2024/07/highlighting-journalism-on-mastodon/

151·5 months ago

151·5 months agoIsn’t Angstrom 10^-10 meters? And nanometers 10^-9 meters? So 20A (assuming A = Angstrom) is just 2nm?

Are they trying to say that by moving to this new era, they’ll go single digit Angstrom i.e., 0.x nm?

Thank you, I’ll send you an email within a day.

I knew about the “Thour” meme, but still didn’t get why the directory turned compressed. My guess is that by licking the lemon, the directory folds in on itself, thus becoming compressed.

Would you consider sending it to Austria? I’d pay shipping charges (if it’s within reason lol). If you are, you can send me an email at:

sneela-hwelemmy92fd [at] port87.com

Are you planning to scrap the CPU? I may be interested in it as I find faulty hardware fun to experiment on.

You haven’t given us much information about the CPU. That is very important when dealing with Machine Check Errors (MCEs).

I’ve done a bit of work with MCEs and AMD CPUs, so I’ll help with understanding what may be going wrong and what you probably can do.

I’ve done a bit of searching from the microcode & the Dell Wyse thin client that you mentioned. From what I can garner, are you using a Dell Wyse 5060 Thin Client with an AMD steppe Eagle GX-424 [1]? This is my assumption for the rest of this comment.

Machine Check Errors (MCEs) are hard to decipher find out without the right documentation. As far as I can tell from AMD’s Data Sheet for the G-Series [2], this CPU belongs to family 16H.

You have two MCEs in your image:

- CPU Core 0, Bank 4: f600000000070f0f

- CPU Core 1, Bank 1: b400000001020103

Now, you can attempt to decipher these with a tool I used some time ago, MCE-Ryzen-Decoder [4]; you may note that the name says Ryzen - this tool only decodes MCEs of Ryzen architectures. However, MCE designs may not change much between families, but I wouldn’t bank (pun not intended) on it because it seems that the G-Series are an embedded SOC compared to the Ryzen CPUs which are not. I gave it a shot and the tool spit out that you may have an issue in:

$ python3 run.py 04 f600000000070f0f Bank: Read-As-Zero (RAZ) Error: ( 0x7) $ python3 run.py 01 b400000001020103 Bank: Instruction Fetch Unit (IF) Error: IC Full Tag Parity Error (TagParity 0x2)Wouldn’t bank (pun intended this time) on it though.

What you can do is to go through the AMD Family 16H’s BIOS and Kernel Developer Guide [3] (Section 2.16.1.5 Error Code). From Section 2.16.1.1 Machine Check Registers, it looks like Bank 01 corresponds to the IC (Instruction Cache) and Bank 04 corresponds to the NB (Northbridge). This means that the CPU found issues in the NB in core 0 and the IC in core 1. You can go even further and check what those exact codes decipher to, but I wouldn’t put in that much effort - there’s not much you can do with that info (maybe the NB, but… too much effort). There are some MSRs that you can read out that correspond to errors of these banks (from Table 86: Registers Commonly Used for Diagnosis), but like I said, there’s not much you can do with this info anyway.

Okay, now that the boring part is over (it was fun for me), what can you do? It looks like the CPU is a quad core CPU. I take it to mean that it’s 4 cores * 2 SMT threads. If you have access to the linux command line parameters [5], say via GRUB for example, I would try to isolate the two faulty cores we see here: core 0 and core 1. Add

isolcpus=0,1to see the kernel boots. There’s a good chance that we see only two CPU cores failing, but others may also be faulty but the errors weren’t spit out. It’s worth a shot, but it may not work.Alternatively, you can tell the kernel to disable MCE checks entirely and continue executing; this can be done with the

mce=offcommand line parameter [6] . Beware that this means that you’re now willingly running code on a CPU with two cores that have been shown to be faulty (so far).isolcpuswill make sure that the kernel doesn’t execute any “user” code on those cores unless asked to (viatasksetfor example)Apart from this, like others have pointed out, the red dots on the screen aren’t a great sign. Maybe you can individually replace defective parts, or maybe you have to buy a new machine entirely. What I told you with this comment is to check whether your CPU still works with 2 SMT threads faulty.

Good luck and I hope you fix your server 🤞.

Edited to add: I have seen MCEs appear due to extremely low/high/fluctuating voltages. As others pointed out, your PSU or other components related to power could be busted.

[4] https://github.com/DimitriFourny/MCE-Ryzen-Decoder

[5] https://www.kernel.org/doc/html/latest/admin-guide/kernel-parameters.html

[6] https://elixir.bootlin.com/linux/v6.9.2/source/Documentation/arch/x86/x86_64/boot-options.rst

The debug version you compile doesn’t affect the code; it just stores more information about symbols. The whole shtick about the debugger replacing instructions with INT3 still happens.

You can validate that the code isn’t affected yourself by running objdump on two binaries, one compiled with debug symbols and one without. Otherwise if you’re lazy (like me 😄):

https://stackoverflow.com/a/8676610

And for completeness: https://gcc.gnu.org/onlinedocs/gcc-14.1.0/gcc/Debugging-Options.html

Excellent question!

Before replacing the instruction with INT 3, the debugger keeps a note of what instruction was at that point in the code. When the CPU encounters INT 3, it hands control to the debugger.

When the debugging operations are done, the debugger replaces the INT 3 with the original instruction and makes the instruction pointer go back one step, thereby ensuring that the original instruction is executed.

This you?

https://lemmy.world/post/10541551